# TECHNICAL DATA VT-DRM(S) VT01RADFET Readout Module

# Features

- Comprises:

- o two 400 nm RADFETs

- o two 100 nm RADFETs

- Temperature endurance range: -40°C to +85°C

- Onboard temperature sensor

- Maximum sensitivity: 130 mV/Gy

- Dimensions: 35 mm x 50 mm x 7 mm

- Communication: Standard SPI or isoSPI on distance up to 100 m

# Description

Designed in partnership with the European Space Agency (ESA), VT-DRM(S) is a total ionizing dose (TID) measuring module aimed at providing an optimized RADFET read-out for various RADFET technologies. The VT-DRM(S) utilizes 100 nm and 400 nm RADFETs in various sense modes, covering both read-out and irradiation (sense) mode.

The module outputs a digitized threshold voltage, which is directly related to accumulated radiation dose. Designed to compensate for threshold voltage drift due to temperature, VT-DRM(S) provides a stable readout over a large temperature span. VT-DRM(S) can be easily integrated with the host. VT-DRM(S) communicates with the host via standard SPI protocol or isoSPI.

### Typical applications

- Satellites

- Accelerator facilities

- Nuclear power stations

- General purpose radiation detection

## Connector Assignment and Dimensions

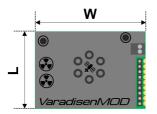

VT-DRM(S) connector assignment and PCB outline drawing are given in Figure 1, and pin description in Table 1.

| Parameter | Min | Typical | Max  |

|-----------|-----|---------|------|

| Width     | -   | 50mm    | -    |

| Length    | -   | 35mm    | -    |

| Height    | -   | 7mm     | 10mm |

| Weight    | 10g | TBM     | TBM  |

Figure 1 VT-DRM(S) connector assignment and PCB outline drawing and dimensions.

| No.    | Pin name | Pin type         | Description / Recommendations                                                                         |  |

|--------|----------|------------------|-------------------------------------------------------------------------------------------------------|--|

| 1      | Va       | POWER            | Analog positive power supply, this pin must be decoupled with 10 $\mu$ F ceramic, low ESR capacitor.  |  |

| 2      | Vdd      | POWER            | Digital positive power supply, this pin must be decoupled with 10 $\mu$ F ceramic, low ESR capacitor. |  |

| 3      | GND      | GND              | Connect to power supply ground.                                                                       |  |

| 4      | Din      | Digital IN       | Serial Data Input                                                                                     |  |

| 5      | CS       | Digital IN       | Chip select; active low                                                                               |  |

| 6      | DOUT     | Digital OUT      | Serial data output combined with data ready; active low                                               |  |

| 7      | SYNC     | Digital IN       | Start conversion                                                                                      |  |

| 8      | SCLK     | Digital IN       | Serial clock input                                                                                    |  |

| 9      | GND      | GND              | Connect to power supply ground.                                                                       |  |

| isoSPI | Im       | Analog<br>In/out | Isolated Interface Minus Input/Output.                                                                |  |

| isoSPI | Рр       | Analog<br>In/out | Isolated Interface Plus Input/Output                                                                  |  |

#### Table 1: Pin description

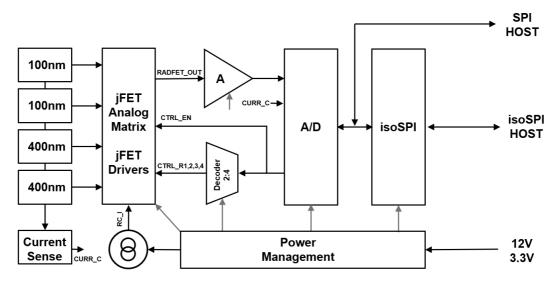

# **Block Diagram**

The schematic diagram of the VT-DRM(S) module is shown in Figure 2.

Figure 2: VT-DRM(S) schematic diagram.

# **Operation Principle**

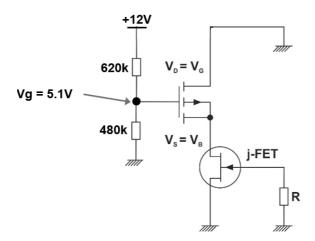

The main sensing elements of the VT-DRM(S) readout module are the RADFET parts, in two oxide thickness variants of 100nm and 400nm thus, two different sensitivities. Each RADFET part consists of two identical transistors, R1 and R2, and a diode. The VT-DRM(S) can be irradiated in active(powered) and passive (unpowered, Va=Vdd=0V) mode. Irradiation (sense) and Read-out modes are implemented by a series of analog switches (j-FETs), providing appropriate biasing conditions.

### Read-Out Mode (Accumulated Radiation Dose Read-Out)

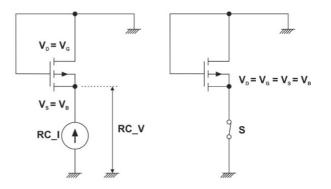

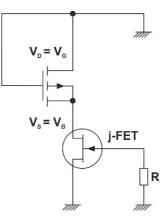

Readout mode (RADFET selection) is set by control signals CTRL\_EN, CTRL\_R1,2,3,4 generated from the ADC. In Irradiation mode, all RADFET terminals are grounded. In Read-out mode, the selected RADFET is biased in Reader Circuit configuration – Drain/Gate tied together and grounded, Source/Bulk tied together, constant DC current source connected to Source/Bulk, RADFET Reader Circuit threshold voltage (RC\_V =  $V_{TH}$ ) read at Source/Bulk.

The current source on VT-DRM(S) is optimized for stability and its current level RC\_I to minimize temperature drift. The  $V_{TH}$  signal is multiplexed, buffered, and filtered, available at (RADFET\_OUT) for digitalisation by the ADC.

The device may be read at arbitrary intervals, depending on the application. The period between readings should be from seconds to days or even months. The circuit used to read out the chip should be similar to the circuit shown below and should be read in connection with the configuration table.

Figure 3: VT-DRM(S) rider circuit configuration.

#### Irradiation Mode (Sense Mode)

Figure 4 VT-DRM(S) zero bias during irradiation (sense mode)

Figure 5: VT-DRM(S) +Vg bias during irradiation (sense mode)

# RADFET Output Values and Timing

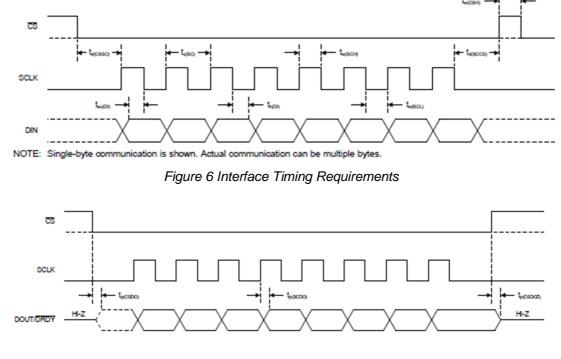

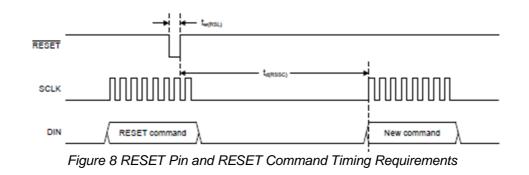

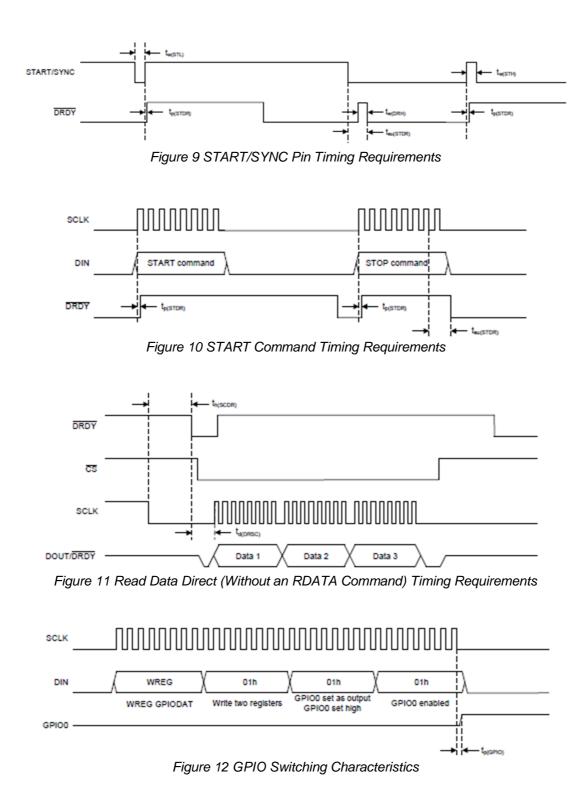

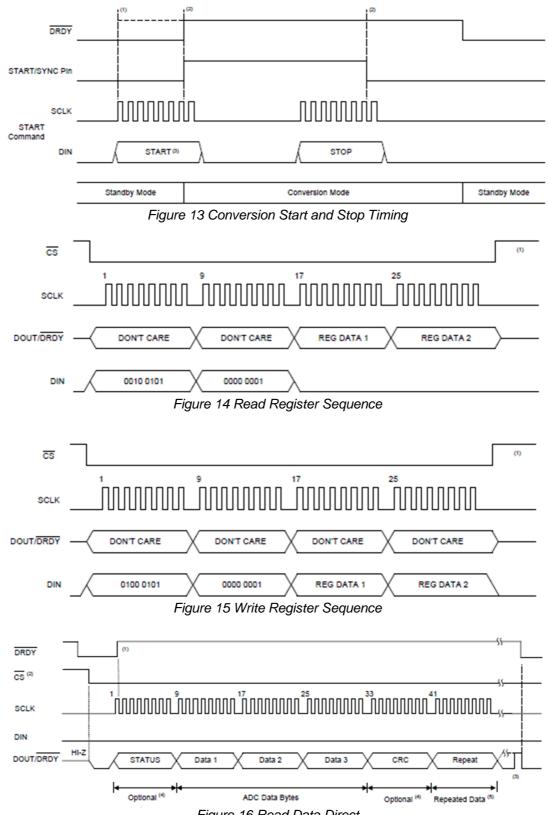

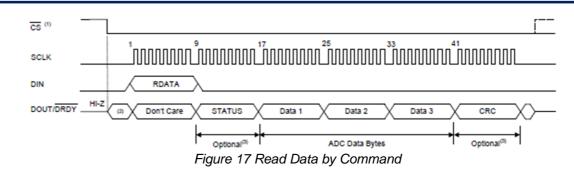

The main component responsible for communication with the host is the SPI interface of the ADS124S06 analog to digital converter. The ADS124S06 has a 3-wire or 4-wire SPI interface that is compatible with various DSP units.

The SPI-compatible serial interface is used to read the conversion data and also to configure and control the ADC. The serial interface consists of four signals: CS, SCLK, DIN, and DOUT/DRDY. The conversion data are provided with an optional CRC code for improved data integrity. The dual function DOUT/DRDY output indicates when conversion data are ready and also provides the data output. The serial interface can be implemented with as little as three connections by tying CS low. Start ADC conversions with either the START/SYNC pin or with commands. The ADC can be programmed for a continuous conversion mode or to perform single-shot conversions.

The module can be configured in different read-out/conversion modes, more details in the following Figures:

Figure 7 Serial Interface Switching Characteristics

Figure 16 Read Data Direct

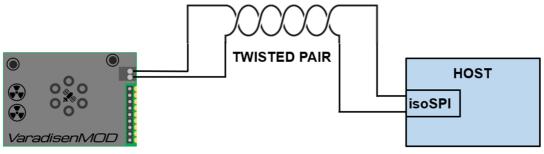

The isoSPI communication is establish by the LTC6820 chip which provides bidirectional SPI communications between two isolated devices through a single twisted pair connection. Each LTC6820 encodes logic states into signals that are transmitted across an isolation barrier to another LTC6820.

Figure 18: isoSPI connection with HOST.

# Radiation Calibration Data

TID > 50 Gy (5 kRad)

Contact: <a href="mailto:support@varadis.com">support@varadis.com</a> for more details.

# Recommended Operating Conditions

VT-DRM(S) module recommended operating conditions are given in Table 4.

| Symbol | Parameter                                            | Value   | Unit |

|--------|------------------------------------------------------|---------|------|

| Vdd    | Supply voltage, referenced to GND                    | 3.3 V   | V    |

| Va     | Supply voltage, referenced to GND                    | 12V     | V    |

| Din    | Serial Data Input                                    | Vdd-0.2 | V    |

| CS     | Chip Select Input                                    | Vdd-0.2 | V    |

| DOUT   | Serial Data Output/Data Ready Output                 | Vdd-0.2 | V    |

| SYNC   | Synchronization Input                                | Vdd-0.2 | V    |

| SCLK   | Serial Data Input to the Input Shift Register on the | Vdd-0.2 | V    |

|        | module                                               |         |      |

| GND    | Supply ground                                        | 0       | V    |

| Im     | Isolated Interface Minus Input/Output                | -       | V    |

| Рр     | Isolated Interface Plus Input/Output                 | -       | V    |

| Т      | Ambient operating temperature                        | 22      | °C   |

| ARH    | Ambient relative humidity (non-condensant)           | < 85    | %    |

#### Table 2: Recommended Operating Conditions

# DC Electrical Characteristics

VT-DRM(S) module DC electrical characteristics are given in Table 3.

| Parameter                                  | Min            | Typical     | Max  |

|--------------------------------------------|----------------|-------------|------|

| Digital supply                             | 2.7 V          | 3.3 V       | 3.6V |

| Analog supply                              | 11V            | 12V         | 15V  |

| Current consumption reading mode           | 0              | 5mA         | 10mA |

| Current consumption sense mode             | 0 <sup>1</sup> | 100nA       | 30uA |

| Sensitivity <sup>2</sup> 100nm Zero Biased |                | 1.5 mV/Gy   |      |

| Sensitivity 100nm +Gate Biased             |                | 5.96mV/Gy   |      |

| Sensitivity 400nm Zero Biased              |                | 0.55 mV/cGy |      |

| Sensitivity 400nm +Gate Biased             |                | 130mV/Gy    |      |

| Total ionising dose                        | 1cGy           |             | 1kGy |

| Temperature range                          | -55 C          | 20 C        | 85 C |

| Measurement interval                       | 15sec          | 2min        | 1Day |

Table 3: DC electrical characteristics

<sup>&</sup>lt;sup>1</sup> In case of unpowered module, when Va=Vdd=0V

<sup>&</sup>lt;sup>2</sup> The sensitivity decreases with the received dose, the given typical sensitivity is extracted from the linear region (beginning of radiation)

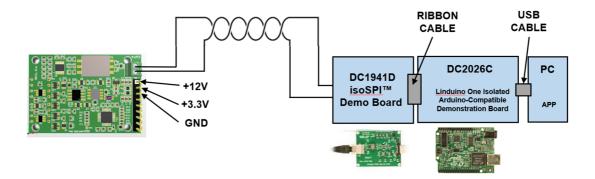

# isoSPIDemoCircuitInterface

In the following diagram a demo connection with a host using development kits DC1941D isoSPI<sup>™</sup> Demo Board and DC2026C, Linduino One Isolated Arduino-Compatible Demonstration Board:

Figure 19: isoSPI example connection with PC.

# Soldering and Mounting

It is important that the VT-DRM(S) is the last component to be hand soldered onto a circuit board. If a different soldering profile is required, please contact us at support@varadis.com. VT-DRM(S) can be soldered directly on the customer PCB (treated as SMD) or via standard through hole 10-pin header connector with a pitch of 2.54 mm; example (Mfr. No: 1-826629-0). Recommended dimensions for solder pad layout are given in Figure 7.

# Handling

All assembled boards undergo 100% electrical test and visual inspection immediately prior to shipment. Therefore, all boards should reach the customer in excellent condition. To ensure that the boards remain in this condition, please handle the parts as carefully as possible and observe standard precautions related to ESD sensitive devices.

## Notes

Varadis Ltd and its subsidiaries reserve the right to make changes, corrections, enhancements, modifications, and improvements to Varadis products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on Varadis products before placing orders. Varadis products are sold pursuant to the Varadis terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of Varadis products and Varadis assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by Varadis herein. Resale of Varadis products with provisions different from the information set forth herein shall void any warranty granted by Varadis for such product.

Varadis and the Varadis logo are trademarks of Varadis. All other product or service names are the property of their respective owners. Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 Varadis Ltd – All rights reserved